## Wie errechnen sich die Ausgangsfrequenzen des LeoBodnar GPSDO?

Die Windows Software zum Einstellen der (beiden) Output-Frequenzen des LeoBodnar GPSDO ist, was die Berechnung der Ausgangsfrequenzen angeht, nicht gerade "selbsterklärend".

Nach ein bisschen Recherche im Web fand ich die erleuchtenden Hinweise :-)

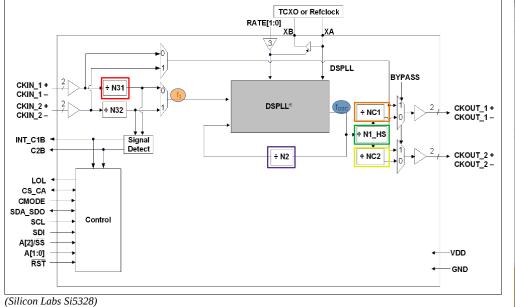

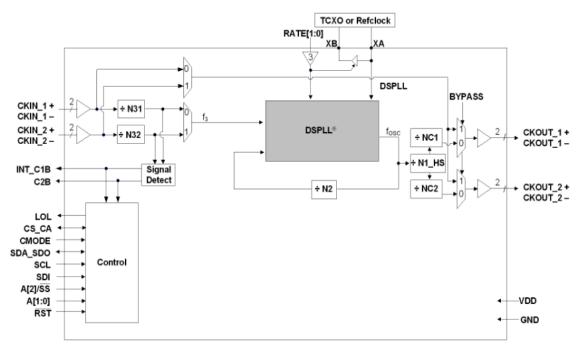

Um die verschiedenen Ausgangsfrequenzen zu erzeugen wird ein Baustein zur Vervielfachung des vom GPS-Signal abgeleiteten Taktes von Silicon Labs verbaut. Beim GPSDO mit zwei Clock Ports ist es der Si5328 (vermutlich auch bei dem Single Port GPSDO).

Beim Blick auf das Blockschaltbild des Si5328 erklärt sich sofort die vom LeoBodnar GPSDO verwendeten Bezeichner der einzelnen Parameter.

Hier erklärt sich nun auch wie die beiden Ausgangstakte (NCx\_LS [1, 2, 4, 6, ..., 2^20]) zusammen hängen.

Beide Takte leiten sich von der gemeinsamen Quelle "N1\_HS" ab (N1\_HS = Highspeed Devider [4, 5, ..., 11]).

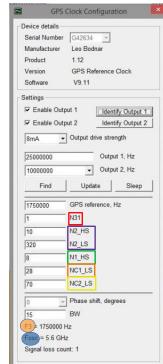

Ich habe zur Zeit 25MHz (Output 1) und 10MHz (Output 2) im GPSDO eingestellt.

Rechnet man die Frequenzen zurück ergibt sich für N1\_HS folgende Frequenz:

- → 25MHz x 28 = 700MHz

- → 10MHz x 70 = 700MHz

Diese 700MHz wiederum errechnen sich aus der fosc und dem Teiler N1\_HS (4, 5, ..., 11):

→  $700MHz \times 8 = 5,6GHz$

Die Oszilatorfrequenz errechnet sich indem wir die Eingangsfrequenz f3 mit dem Divider N2 (N2 = N2\_HS x N2\_LS) multiplizieren (f Osc = 4.85GHz – 5.67GHz !).

$\rightarrow$  1750000Hz x (10 x 320) = 5,6GHz!

Dabei gelten folgende Divider:

- → N2\_HS = 4, 5, ..., 11

- $\rightarrow$  N2 LS = 2, 4, 6, ...,  $2^2$

Der Teiler N31 hat hier den Wert "1". Somit ist die Frequenz f3 gleich der Eingangsfrequenz!

## 3.9. Si5328

The Si5328 is a jitter-attenuating precision clock multiplier for applications requiring sub-1 ps jitter performance and digitally-programmable ultra-low-loop BW ranging from 0.05 to 6 Hz. When combined with a low-wander, low-jitter reference oscillator, the Si5328 meets all of the wander, MTIE, TDEV, and other requirements that are listed in ITU-T G.8262. The Si5328 accepts two input clocks ranging from 8 kHz to 346 MHz and generates two output clocks ranging from 2 kHz to 346 MHz. The device provides virtually any frequency translation combination across the operating range. The Si5328 input clock frequency and clock multiplication ratio are programmable through and I<sup>2</sup>C or SPI interface. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5328 is ideal for providing multiplication and jitter/wander attenuation in high-performance timing applications like SyncE timing cards. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description. Also see "AN775: Si5328 ITU-T G.8261 SyncE Compliance Test Report" and "AN776: Using the Si5328 in a G.8262 Compliant SyncE Application".

Figure 9. Si5328 Clock Multiplier and Jitter Attenuator Block Diagram

**Table 26. Narrowband Frequency Limits**

| Signal         | Frequency Limits                 |  |

|----------------|----------------------------------|--|

| CKINn          | 2 kHz-710 MHz                    |  |

| f <sub>3</sub> | 2 kHz-2 MHz                      |  |

| fosc           | 4.85-5.67 GHz                    |  |

| fout           | f <sub>OUT</sub> 2 kHz-1.475 GHz |  |

Note: Fmax = 346 MHz for the Si5328 and 808 MHz for the Si5327, Si5374, Si5375, and Si5376. Each entry has 500 ppm margins at both ends. The Si5374, Si5375, and Si5376 have an extend Fosc range of from 4.6 to 6 GHz.

Table 27. Dividers and Limits

| Divider | Equation            | Si5325, Si5367                                                  | Si5319, Si5324, Si5326, Si5327,<br>Si5328, Si5368, Si5369, Si5374,<br>Si5375, Si5376 |

|---------|---------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|

| N1      | N1 = N1_HS x NCn_LS | N1_HS = [4, 5,, 11]<br>NCn_LS = [1, 2, 4, 6,, 2 <sup>20</sup> ] | N1_HS = [4, 5,, 11]<br>NCn_LS = [1, 2, 4, 6,, 2 <sup>20</sup> ]                      |

| N2      | N2 = N2_HS x N2_LS  | N2_LS = [32, 34, 36,, 2 <sup>9</sup> ]                          | N2_HS = [4, 5,, 11]<br>N2_LS = [2, 4, 6,, 2 <sup>20</sup> ]                          |

| N3      | N3 = N3n            | N3n = [1,2,3,,2 <sup>19</sup> ]                                 | N3n = [1,2,3,,2 <sup>19</sup> ]                                                      |

Rev. 1.3 65